- 您现在的位置:买卖IC网 > Sheet目录2002 > KAD5512HP-17Q72 (Intersil)IC ADC 12BIT 170MSPS SGL 72-QFN

23

FN6808.3

October 1, 2009

SPI Physical Interface

The serial clock pin (SCLK) provides synchronization for the

data transfer. By default, all data is presented on the serial

data input/output (SDIO) pin in three-wire mode. The state of

the SDIO pin is set automatically in the communication

protocol (described in the following). A dedicated serial data

output pin (SDO) can be activated by setting 0x00[7] high to

allow operation in four-wire mode.

The SPI port operates in a half duplex master/slave

configuration, with the KAD5512HP functioning as a slave.

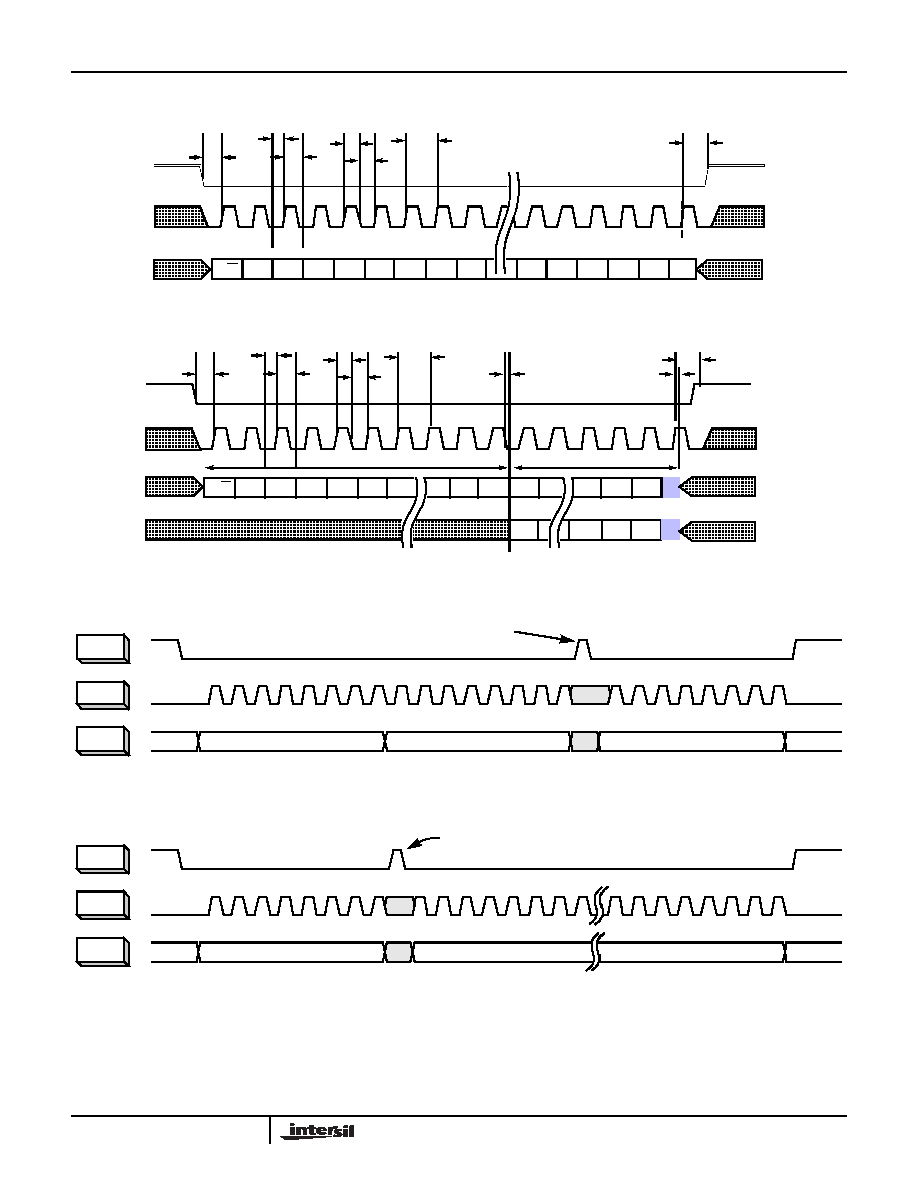

FIGURE 35. SPI WRITE

tS

tHI

tCLK

tLO

R/W

W1

W0

A12 A11 A10

A9

A8

A7

D5

D4

D3

D2

D1

D0

tH

tDHW

tDSW

SPI WRITE

CSB

SCLK

SDIO

FIGURE 36. SPI READ

(3 WIRE MODE)

(4 WIRE MODE)

R/W

W1

W0

A12 A11 A10

A9

A2

A1

D7

D6

D3

D2

D1

D7

D3

D2

D1 D0

A0

WRITING A READ COMMAND

READING DATA

D0

tH

tDHR

tDVR

SPI READ

tHI

tCLK

tLO

tDHW

tDSW

tS

CSB

SCLK

SDIO

SDO

FIGURE 37. 2-BYTE TRANSFER

CSB

SCLK

SDIO

INSTRUCTION/ADDRESS

DATA WORD 1

DATA WORD 2

CSB STALLING

FIGURE 38. N-BYTE TRANSFER

CSB

SCLK

SDIO

INSTRUCTION/ADDRESS

DATA WORD 1

DATA WORD N

LAST LEGAL

CSB STALLING

KAD5512HP

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

KAD5512P-17Q72

IC ADC 12BIT 170MSPS SGL 72-QFN

KAD5514P-12Q72

IC ADC 14BIT 125MSPS SGL 72-QFN

KAD5610P-25Q72

IC ADC 10BIT 250MSPS DUAL 72-QFN

KAD5612P-17Q72

IC ADC 12BIT 170MSPS DUAL 72-QFN

LA72715NV-TLM-E

IC AUDIO DECODER JPN MTS 24SSOP

LICAL-DEC-LS001

IC DECODER LOW SECURITY 8DIP

LICAL-DEC-MS001

IC DECODER MS SERIES 20-SSOP

LICAL-ENC-MS001

IC ENCODER MS SERIES 20-SSOP

相关代理商/技术参数

KAD5512HP-21Q48

功能描述:模数转换器 - ADC 12-BIT 210MSPS HI PERF SINGLE ADC PROG

RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32

KAD5512HP-21Q72

功能描述:模数转换器 - ADC 12-BIT 210MSPS HI PERF SINGLE ADC PROG

RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32

KAD5512HP-25Q48

功能描述:模数转换器 - ADC 12-BIT 250MSPS HI PERF SINGLE ADC

RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32

KAD5512HP-25Q72

功能描述:模数转换器 - ADC 12-BIT 250MSPS HI PERF SINGLE ADC

RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32

KAD5512P

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Low Power 12-Bit, 250/210/170/125MSPS ADC

KAD5512P_09

制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Low Power 12-Bit, 250/210/170/125MSPS ADC

KAD5512P-12Q48

功能描述:模数转换器 - ADC 12-BIT 125MSPS SINGL ADC PROG LVDS/LVCMOS RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32

KAD5512P-12Q72

功能描述:模数转换器 - ADC 12-BIT 125MSPS SINGL ADC PROG LVDS/LVCMOS RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32